## CS8N65FA9R-G

## **General Description:**

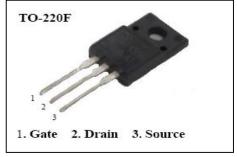

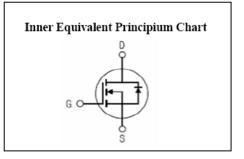

CS8N65F A9R-G, the silicon N-channel Enhanced VDMOSFETs, is obtained by the self-aligned planar Technology which reduce the conduction loss, improve switching performance and enhance the avalanche energy. The transistor can be used in various power switching circuit for system miniaturization and higher efficiency. The package form is TO-220F, which accords with the RoHS standard.

| Fea | f11 | rec |   |

|-----|-----|-----|---|

| rta | ւս  | 169 | 2 |

- I Fast Switching

- I Low ON Resistance(Rdson≤1.0Ω)

- I Low Gate Charge (Typical Data:29nC)

- 1 Low Reverse transfer capacitances(Typical:6.6pF)

- I 100% Single Pulse avalanche energy Test

- I Halogen Free

## **Applications:**

Power switch circuit of adaptor and charger.

**Absolute** (Tc=  $25^{\circ}$ C unless otherwise specified):

| $V_{DSS}$              | 650  | V |

|------------------------|------|---|

| $I_D$                  | 8    | A |

| $P_D(T_C=25^{\circ}C)$ | 38   | W |

| $R_{DS(ON)Typ}$        | 0.86 | Ω |

| Symbol                            | Parameter                                        | Rating          | Units        |

|-----------------------------------|--------------------------------------------------|-----------------|--------------|

| $V_{\mathrm{DSS}}$                | Drain-to-Source Voltage                          | 650             | V            |

| Continuous Drain Current          |                                                  | 8               | A            |

| $I_{D}$                           | Continuous Drain Current T <sub>C</sub> = 100 °C | 5               | A            |

| I <sub>DM</sub> a1                | Pulsed Drain Current                             | 32              | A            |

| $V_{GS}$                          | Gate-to-Source Voltage                           | ±30             | V            |

| E <sub>AS</sub> a2                | Single Pulse Avalanche Energy                    | 500             | mJ           |

| dv/dt <sup>a3</sup>               | Peak Diode Recovery dv/dt                        | 5.0             | V/ns         |

| P <sub>D</sub>                    | Power Dissipation                                | 38              | W            |

|                                   | Derating Factor above 25°C                       | 0.3             | W/℃          |

| T <sub>J</sub> , T <sub>stg</sub> | Operating Junction and Storage Temperature Range | 150, -55 to 150 | $^{\circ}$ C |

| $T_{L}$                           | Maximum Temperature for Soldering                | 300             | $^{\circ}$   |