STRUCTURE Silicon Monolithic Integrated Circuit

NAME OF PRODUCT DC-AC Inverter Control IC

TYPE BD9897FS

FUNCTION • 36V High voltage process

1ch control with Full-Bridge

· Lamp current and voltage sense feed back control

· Sequencing easily achieved with Soft Start Control

· Short circuit protection with Timer Latch

Under Voltage Lock Out

· Mode-selectable the operating or stand-by mode by stand-by pin

· Synchronous operating the other BD9897FS IC's

· BURST mode controlled by PWM and DC input

· Output liner Control by external DC voltage

#### ○Absolute Maximum Ratings (Ta = 25°C)

| Parameter                    | Symbol | Limits          | Unit |

|------------------------------|--------|-----------------|------|

| Supply Voltage               | Vcc    | 36              | ٧    |

| BST pin                      | BST    | 40              | V    |

| SW pin                       | SW     | 36              | V    |

| BST-SW voltage difference    | BST-SW | 7               | ٧    |

| Operating Temperature Range  | Topr   | -40~+85         | c    |

| Storage Temperature Range    | Tstg   | <b>-55∼+150</b> | Ĉ    |

| Maximum Junction Temperature | Tjmax  | +150            | C    |

| Power Dissipation            | Pd     | 950*            | mW   |

\*Pd derate at 7.6mW/°C for temperature above Ta = 25°C (When mounted on a PCB 70.0mm×70.0mm×1.6mm)

#### Operating condition

| Parameter                 | Symbol | Limits    | Unit |

|---------------------------|--------|-----------|------|

| Supply voltage            | Vcc    | 7.5~30.0  | V    |

| BST voltage               | BST    | 4.0~36.0  | ٧    |

| BST-SW voltage difference | BST-SW | 4.0~6.5   | ٧    |

| CT oscillation frequency  | fcT    | 60~180    | kHz  |

| BCT oscillation frequency | fвст   | 0.05~1.00 | kHz  |

Status of this document

The Japanese version of this document is the official specification.

Please use the translation version of this document as a reference to expedite understanding of the official version.

If these are any uncertainty in translation version of this document, official version takes priority.

# ○ Electric Characteristics (Ta=25°C, VCC=24V)

| Parameter                                                              |                                  |                  | Limits        |                |           |                                  |  |

|------------------------------------------------------------------------|----------------------------------|------------------|---------------|----------------|-----------|----------------------------------|--|

| T d ramoto.                                                            | Symbol                           | MIN.             | TYP.          | MAX.           | Unit      | Cond it i ons                    |  |

| ((WHOLE DEVICE))                                                       |                                  |                  |               |                |           |                                  |  |

| Operating current                                                      | Icc1                             | _                | 7.2           | 13             | mA        | CT_SYNC_IN = OPEN                |  |

| Stand-by current                                                       | Icc2                             | _                | 13.0          | 30.0           | μΑ        |                                  |  |

| ((STAND BY CONTROL))                                                   | V                                | 0.0              | ı             | 1/00           | ,         | 1001                             |  |

| Stand-by voltage H                                                     | VstH<br>VstL                     | 2.0<br>-0.3      |               | VCC<br>0.8     | V         | System ON System OFF             |  |

| Stand-by voltage L<br>((UVLO BLOCK)))                                  | VSTL                             | -0.3             |               | 0.8            | · ·       | System OFF                       |  |

| Operating voltage (VCC)                                                | Vuv I oH                         | 5.7              | 6.0           | 6.3            | V         | T                                |  |

| Hesteresis width (VCC)                                                 | ⊿VCC_VuvIo                       | 0.26             | 0.35          | 0.43           | ٧         |                                  |  |

| Operating voltage (UVLO)                                               | Vuv I o2                         | 2.179            | 2.25          | 2.321          | ٧         |                                  |  |

| Hesteresis width (UVL0)                                                | ⊿Vuvlo                           | 0.074            | 0.098         | 0.122          | ٧         |                                  |  |

| ((REG BLOCK))                                                          |                                  |                  |               |                |           |                                  |  |

| REG output voltage                                                     | VREG                             | 5.68             | 5.80          | 5.92           | ٧         | VCC>7.0V                         |  |

| REG source current                                                     | IREG                             | 20.0             | _             | <del>-</del>   | mA        |                                  |  |

| ((OSC BLOCK)) Active edge setting current                              | lact                             | 1.35/(RT*7)      | 1.5/(RT*6)    | 1.65/(RT*5)    | A         | T                                |  |

| Negative edge setting current                                          | Ineg                             | lact×29          | lact ×35      | lact×41        | Â         | -                                |  |

| OSC Max voltage                                                        | VOSCH                            | 1.8              | 2.0           | 2.2            | v         | fCT=120kHz                       |  |

| OSC Min voltage                                                        | VOSCL                            | 0.35             | 0.45          | 0.60           | V         | fCT=120kHz                       |  |

| Soft start current                                                     | ISS                              | 0.6              | 1.1           | 1.6            | μΑ        |                                  |  |

| SRT ON resistance                                                      | RSRT                             |                  | 100           | 200            | Ω         |                                  |  |

| ((BOSC BLOCK))                                                         |                                  |                  |               |                |           |                                  |  |

| BOSC Max voltage                                                       | VBCTH                            | 1.94             | 2.00          | 2.06           | V         | fBCT=0. 3kHz                     |  |

| BOSC Min voltage                                                       | VBCTL                            | 0, 40            | 0.50          | 0,60           | v         | fBCT=0. 3kHz                     |  |

| BOSC constant current                                                  | IBCT                             | 1.35/BRT         | 1.5/RT        | 1.65/RT        | Ā         | VBCT=0.2V                        |  |

| BOSC frequency                                                         | fBCT                             | 291              | 300           | 309            | Hz        | (BRT=33k Ω BCT=0.048 μF)         |  |

| ((FEED BACK BLOCK))                                                    | 1501                             | 231              | 300           | 303            | L 112     | (5111-338 \$2 601-0: 040 \(\mu\) |  |

|                                                                        | VIST                             | 1.225            | 1, 250        | 1.275          | l v       | T                                |  |

| IS threshold voltage 1                                                 |                                  | 1.223            |               |                |           | l                                |  |

| IS threshold voltage 2                                                 | VIS2                             | _                | VREFIN        | VIS①           | ٧         | VREF applying voltage            |  |

| VS threshold voltage                                                   | VVS                              | 1.220            | 1.250         | 1.280          | ٧         |                                  |  |

| IS source current 1                                                    | 1181                             | _                | _             | 0.9            | μA        | DUTY=2.2V                        |  |

| IS source current 2                                                    | 1182                             | 32               | 50            | 68             | μA        | DUTY=0V IS=0.5V                  |  |

| VS source current IS COMP detect voltage ①                             | IVS<br>VISCOMP①                  | 0.90             | 0.94          | 0.9<br>0.98    | μA<br>V   | VREFIN≧1.25V                     |  |

| IS COMP detect voltage ②                                               | VISCOMP2                         | - 0.30           | VREF1N×0.73   |                | l v       | VREFIN<1.25V                     |  |

| VREF input voltage range                                               | VREFIN                           | 0.6              | _             | 1.6            | v         | No effect at VREF>1.25V          |  |

| ((DUTY BLOCK))                                                         |                                  |                  |               |                |           |                                  |  |

| High voltage                                                           | VDUTY-OUTH                       | 2.8              | 3.1           | 3. 4           | ٧         |                                  |  |

| Low voltage                                                            | VDUTY-OUTL                       |                  | -             | 0.5            | ٧         |                                  |  |

| DUTY-OUT sink resistance DUTY-OUT source resistance                    | RDUTY-OUTSink<br>RDUTY-OUTSouce  |                  | 150<br>250    | 300<br>500     | Ω         |                                  |  |

| ((OUTPUT BLOCK))                                                       | 1 15011-00130008                 | L                | 1 230         |                |           | 1                                |  |

| LN output sink resistance                                              | RsinkLN                          | _                | 1.5           | 3.0            | Ω         |                                  |  |

| LN output source resistance                                            | RsourceLN                        | _                | 5             | 10             | Ω         | 1                                |  |

| HN output sink resistance                                              | RsinkHN                          | _                | 2.5           | 5.0            | Ω         | VBST-VSW=5.0V                    |  |

| HN output source resistance                                            | RsourceLN                        | _                | 5             | 10             | Ω         | VBST-VSW=5.0V                    |  |

| MAX DUTY                                                               | MAX DUTY                         | 46.0             | 48.0          | 49.5           | %         | FOUT=60kHz                       |  |

| OFF period Drive output frequency                                      | TOFF<br>FOUT                     | 100<br>58.5      | 200<br>60.0   | 400<br>61.5    | ns<br>kHz | (RT=4.7k Ω CT=235pF)             |  |

| ((TIMER LATCH BLOCK))                                                  | 1 1001                           | 1 30.5           | 1 00.0        | 01.5           | KHZ       | (m1=4.7k12 C1=235pr)             |  |

| Timer Latch setting voltage                                            | VCP                              | 1.94             | 2.0           | 2.06           | ٧         |                                  |  |

| Timer Latch setting current                                            | ICP                              | 0.40             | 0.55          | 0.70           | μA        |                                  |  |

| ((COMP CLOCK))                                                         |                                  |                  |               |                |           |                                  |  |

| COMP1 over voltage detect voltage                                      | VCOMPH                           | 2.460            | 2. 485        | 2.510          | V         | VSS>2.2V                         |  |

| COMP2 over voltage detect voltage COMP2 under voltage detect voltage ① | VCOMP2_H                         | 2.460            | 2.485         | 2.510          | V         | VSS>2.2V                         |  |

| COMP2 under voltage detect voltage ①                                   | VCOMP_L_1<br>VCOMP_L_2           | 1. 225<br>0. 606 | 1.25<br>0.625 | 1.275<br>0.644 | V V       | VSS > 2. 2V<br>VSS < 2. 2V       |  |

| ((Synchronous Block))                                                  |                                  |                  |               |                |           |                                  |  |

| High voltage                                                           | VCT_SYNCH                        | 2.8              | 3.1           | 3.4            | ٧         |                                  |  |

|                                                                        |                                  | _                | _             | 0.5            | ٧         |                                  |  |

| Low voltage                                                            | VCT_SYNCL                        |                  |               |                |           |                                  |  |

| CT_SYNC sink resistance                                                | RCT_SYNC_SYNC                    | -                | 150           | 300            | Ω         |                                  |  |

| CT_SYNC sink resistance<br>CT_SYNC source resistance                   | RCT_SYNC_SYNC<br>RCT_SYNC_SOURCE | _                | 150<br>370    | 300<br>740     | Ω<br>Ω    |                                  |  |

| CT_SYNC sink resistance                                                | RCT_SYNC_SYNC                    |                  |               |                |           |                                  |  |

(This product is not designed to be radiation-resistant.)

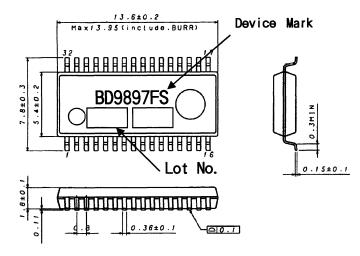

# OPackage Dimensions

# **OPin Description**

SSOP-A32 (Unit:mm)

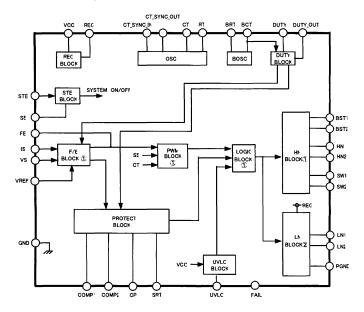

# OBlock Diagram

| PIN<br>No. | PIN NAME    | FUNCTION                                                                       |

|------------|-------------|--------------------------------------------------------------------------------|

| 1          | PGND        | Ground for FET drivers                                                         |

| 2          | LN2         | NMOS FET driver                                                                |

| 3          | HN2         | NMOS FET driver                                                                |

| 4          | SW2         | Lower rail voltage for HN2 output                                              |

| -5         | BST2        | Boot-Strap input for HN2 output                                                |

| 6          | CT_SYNC_IN  | CT synchronous signal input pin                                                |

| 7          | CT_SYNC_OUT | CT synchronous signal output pin                                               |

| 8          | SRT         | External resistor from SRT to RT for adjusting the triangle oscillator         |

| 9          | RT          | External resistor from SRT to RT for adjusting the triangle oscillator         |

| 10         | СТ          | External capacitor from CT to GND for adjusting the triangle oscillator        |

| 11         | GND         | GROUND                                                                         |

| 12         | ВСТ         | External capacitor from BCT to GND for adjusting the BURST triangle oscillator |

| 13         | BRT         | External resistor from BRT to GND for adjusting the BURST triangle oscillator  |

| 14         | DUTY        | Control PWM mode and BURST mode                                                |

| 15         | DUTY_OUT    | BURST signal output pin                                                        |

| 16         | STB         | Stand-by switch                                                                |

| 17         | CP          | External capacitor from CP to GND for Timer Latch                              |

| 18         | FAIL        | COMP2 under voltage protect clock output                                       |

| 19         | VREF        | Reference voltage input pin for Error amplifier                                |

| 20         | vs          | Error amplifier input                                                          |

| 21         | IS          | Error amplifier input                                                          |

| 22         | FB          | Error amplifier output                                                         |

| 23         | SS          | External capacitor from SS to GND for Soft Start<br>Control                    |

| 24         | COMP2       | Under, over voltage detect pin                                                 |

| 25         | COMP1       | Over voltage detect pin                                                        |

| 26         | VCC         | Supply voltage_input                                                           |

| 27         | UVL0        | External Under Voltage Lock Out                                                |

| 28         | REG         | Internal regulator output                                                      |

| 29         | BST1        | Boot-Strap input for HN1 output                                                |

| 30         | SW1         | Lower rail voltage for HN1 output                                              |

| 31         | HN1         | NMOS FET driver                                                                |

| 32         | LN1         | NMOS FET driver                                                                |

#### ONOTE FOR USE

- 1. When designing the external circuit, including adequate margins for variation between external devices and IC. Use adequate margins for steady state and transient characteristics.

- 2. The circuit functionality is guaranteed within of ambient temperature operation range as long as it is within recommended operating range. The standard electrical characteristic values cannot be guaranteed at other voltages in the operating ranges, however the variation will be small.

- 3. Mounting failures, such as misdirection or miscounts, may harm the device.

- 4. A strong electromagnetic field may cause the IC to malfunction.

- 5. The GND pin should be the location within  $\pm 0.3$ V compared with the PGND pin.

- 6. BD9897FS incorporate a built-in thermal shutdown circuit (TSD circuit). The thermal shutdown circuit (TSD circuit) is designed only to shut the IC off to prevent runaway thermal operation. It is not designed to protect the IC or guarantee its operation of the thermal shutdown circuit is assumed.

- 7. Absolute maximum ratings are those values that, if exceeded, may cause the life of a device to become significantly shortened. Moreover, the exact failure mode caused by short or open is not defined. Physical countermeasures, such as a fuse, need to be considered when using a device beyond its maximum ratings.

- 8. About the external FET, the parasitic Capacitor may cause the gate voltage to change, when the drain voltage is switching. Make sure to leave adequate margin for this IC variation.

- 9. On operating Slow Start Control (SS is less than 2.2V), It does not operate Timer Latch.

- 1 0. By STB voltage, BD9897FS are changed to 2 states. Therefore, do not input STB pin voltage between one state and the other state  $(0.8\sim2.0V)$ .

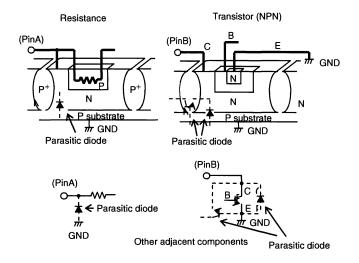

- 1 1. The pin connected a connector need to connect to the resistor for electrical surge destruction. This IC is a monolithic IC which (as shown is Fig-1) has P\* substrate and between the various pins. A P-N junction is formed from this P layer of each pin. For example, the relation between each potential is as follows,

- (When GND > PinB and GND > PinA, the P-N junction operates as a parasitic diode.)

- (When PinB > GND > PinA, the P-N junction operates as a parasitic transistor.)

Parasitic diodes can occur inevitably in the structure of the IC. The operation of parasitic diodes can result in mutual interference among circuits as well as operation faults and physical damage. Accordingly you must not use methods by which parasitic diodes operate, such as applying a voltage that is lower than the GND (P substrate) voltage to an input pin.

- 1 2. This IC is a monolithic IC which (as shown is Fig-1)has P\* substrate and between the various pins. A P-N junction is formed from this P layer of each pin. For example, the relation between each potential is as follows,

- (When GND > PinB and GND > PinA, the P-N junction operates as a parasitic diode.)

- (When PinB > GND > PinA, the P-N junction operates as a parasitic transistor.)

Parasitic diodes can occur inevitably in the structure of the IC. The operation of parasitic diodes can result in mutual interference among circuits as well as operation faults and physical damage. Accordingly you must not use methods by which parasitic diodes operate, such as applying a voltage that is lower than the GND (P substrate) voltage to an input pin.

Fig-1 Simplified structure of a Bipolar IC

#### Notes

- No technical content pages of this document may be reproduced in any form or transmitted by any

means without prior permission of ROHM CO.,LTD.

- The contents described herein are subject to change without notice. The specifications for the

product described in this document are for reference only. Upon actual use, therefore, please request

that specifications to be separately delivered.

- Application circuit diagrams and circuit constants contained herein are shown as examples of standard

use and operation. Please pay careful attention to the peripheral conditions when designing circuits

and deciding upon circuit constants in the set.

- Any data, including, but not limited to application circuit diagrams information, described herein are intended only as illustrations of such devices and not as the specifications for such devices. ROHM CO.,LTD. disclaims any warranty that any use of such devices shall be free from infringement of any third party's intellectual property rights or other proprietary rights, and further, assumes no liability of whatsoever nature in the event of any such infringement, or arising from or connected with or related to the use of such devices.

- Upon the sale of any such devices, other than for buyer's right to use such devices itself, resell or

otherwise dispose of the same, no express or implied right or license to practice or commercially

exploit any intellectual property rights or other proprietary rights owned or controlled by

- ROHM CO., LTD. is granted to any such buyer.

- Products listed in this document are no antiradiation design.

The products listed in this document are designed to be used with ordinary electronic equipment or devices (such as audio visual equipment, office-automation equipment, communications devices, electrical appliances and electronic toys).

Should you intend to use these products with equipment or devices which require an extremely high level of reliability and the malfunction of which would directly endanger human life (such as medical instruments, transportation equipment, aerospace machinery, nuclear-reactor controllers, fuel controllers and other safety devices), please be sure to consult with our sales representative in advance.

It is our top priority to supply products with the utmost quality and reliability. However, there is always a chance of failure due to unexpected factors. Therefore, please take into account the derating characteristics and allow for sufficient safety features, such as extra margin, anti-flammability, and fail-safe measures when designing in order to prevent possible accidents that may result in bodily harm or fire caused by component failure. ROHM cannot be held responsible for any damages arising from the use of the products under conditions out of the range of the specifications or due to non-compliance with the NOTES specified in this catalog.

Thank you for your accessing to ROHM product informations.

More detail product informations and catalogs are available, please contact your nearest sales office.

**ROHM** Customer Support System

THE AMERICAS / EUPOPE / ASIA / JAPAN

www.rohm.com

Contact us : webmaster@rohm.co.jp

Copyright © 2007 ROHM CO.,LTD.

ROHM CO., LTD. 21, Saiin Mizosaki-cho, Ukyo-ku, Kyoto 615-8585, Japan

oan TEL:+81-75-311-2121 FAX:+81-75-315-0172